# Design of New Generation of Binary IO Card for Modular Microprocessor Control System

Zdenek Kehl Department of Power Electronics and Machines University of West Bohemia Pilsen, Czech Republic kehlz@fel.zcu.cz Tomas Glasberger Department of Power Electronics and Machines University of West Bohemia Pilsen, Czech Republic tglasber@fel.zcu.cz Libor Polacek Research and Inovation Centre for Electrical Engineering University of West Bohemia Pilsen, Czech Republic Ipolacek@fel.zcu.cz

Abstract— A new generation of binary input/output card for a modular control system is introduced in this paper. The primary purpose of the proposed binary input/output card is high integration of the number of 32 binary input and output channels. The individual binary channels are designed to fulfill standard industrial control voltage levels. The binary input/output card is designed like a 3U plug-in unit to fit in a standard 3U height 19" sub-rack enclosure. The binary input/output card is equipped with hardware safety and diagnostic features like hardware blocking ability, autodetection, and infrared debug interface. The binary input/output card contains direct system and user signals as well as communications interfaces such as system CAN and user CAN.

## Keywords—channel, binary input, binary output, hardware, blocking, autodetection, microprocessor

#### I. INTRODUCTION

With the progress in power electronics and new topologies of power converters the pressure is growing on requirements of control systems. The new topologies of power converters, especially multilevel converters [1] [2], requires large number of control and diagnostic signals. The measurement of physical quantities is necessary too. These topologies of power converters are usually used in high voltage applications e.q. energy transmission systems like HVDC or photovoltaic systems [3] [4]. In addition, the devices for improving of electrical energy are increasingly being installed in distribution grid. These devices are usually based on high voltage converters with sophisticated topologies [5]. The control systems for these applications have to be reliable and resistant to EMC interference. In addition, it must be able to catch and respond on emergency signals very quickly.

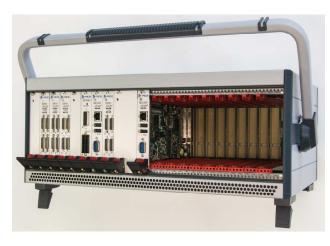

The REMCS (RICE Embedded Modular Control System) was developed to control various industrial applications and power converters. The REMCS is able to control power converters from common topologies as a two-level voltage source inverter up to enhanced modular multi-level topologies such as CHB or M2LC converters. The concept of the control system is based on a multi-card solution, where each microprocessor card can work separately or cooperate. In case of cooperation of individual cards, the 3U sub-rack is used for configuration of the whole REMCS control system. The individual microprocessor cards are MCU, DIF, BIO and AIO. The MCU (Microcontroller Unit) represents the main computer, which serves as interface between REMCS control system and another control or diagnostic system. The MCU card commands all hierarchically lower cards and collect data from them.

Fig. 1. The 3U sub rack solution of REMCS control system [6]

Another REMCS card is DIF (Direct Interface). This card has all the necessary peripherals for independent control of electric drives. The last two cards are BIO (Binary Input/Output card) and AIO (Analog Input/Output card). Both cards expand the number of binary or analog channels of the REMCS. The BIO card is designed to manage industrial control signals. The binary outputs can be used to control power contactors, or they can switch on or switch off some industry devices. This first generation has only 8 channels, which can be configured as 8 binary outputs or 8 binary inputs or 4 binary outputs and 4 binary inputs. Apart from the microprocessor cards, the REMCS contains the Power Supply Unit (PSU) and the Backplane module (BPF). The PSU module was designed to be able to power the whole REMCS. The PSU block represents local power supply unit, which creates supply voltage level 3.3 V and supply voltage level 1.2 V from main supply voltage of 24 V. The PSU unit is designed to input voltage range 16.8 V up to 32 V. It is 30% from nominal supply voltage level. BPF backplane distributes all system and user signals and communications among the other microprocessor cards. BPF module has twenty slots for microprocessor cards and one slot for the PSU module [6].

#### II. FUNCTION DESCRIPTION

The proposed binary IO (BIO) card falls into the second generation of REMCS microprocessor cards. The second generation of the BIO card offers several significant improvements: (i) price optimization; (ii) a 4-times higher number of channels (32 vs. 8) which can be configured as input or output arbitrarily; (iii) each channel can be configured by fitting selected components; (iv) the binary input can be

978-1-6654-9482-3/22/\$31.00 ©2022 IEEE

configured for various voltage levels from 0 up to 150 V DC; (v) the binary output can be set as normally open output, closed output or latched binary output.

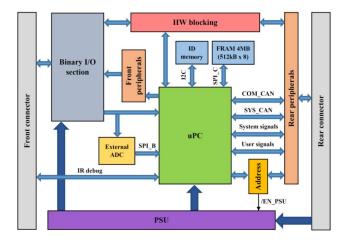

A block diagram of the proposed BIO card is shown in Fig. 2. The central part covering the card's essential intelligence is the Texas Instruments TMS320F28379S microprocessor. It is equipped with external ID memory and FRAM memory. All important information about the given card, such as part number, configuration, date of manufacture etc., are saved in the ID memory. The FRAM memory creates storage for user data.

The microprocessor communicates with another REMCS cards using CAN bus. There are two CAN buses: system CAN bus (SYS\_CAN) and user CAN bus (COM\_CAN). The system CAN bus is used for communication among the IDN (identification) microprocessors, which share the system data among the individual cards. The user CAN bus is available for application level of software. In addition to communications, there are also direct system signals and user signals.

Fig. 2. Block diagram of proposed BIO card

Every module card in REMCS has its address. These addresses are defined by the position of individual cards in the sub-rack back-plane connector. The block Address contains a timing circuit that creates a switching delay on the local PSU of individual cards in the sub-rack. This timing prevents a current peak when the whole system is switched on. The External ADC block expands internal ADCs of the microprocessor. There is an additional eight channels, 16bit ADC. With the internal microprocessor's ADCs, it is possible to measure 32 analog channels.

#### III. MECHANICAL CONCEPT OF BIO CARD

The hardware concept of the BIO card is based on standard Eurocard format which defines its dimensions to 100 mm high and 220mm wide. The signal connectors are placed on both sides of the PCB. All of the 62 terminals are connected through a front panel D-SUB connector. The front panel contains eight signalization LEDs that indicate the card's specific states. One user LED signal is mapped to the GPIO pin of the microprocessor. The front panel is also equipped with an infrared port for communication with the microprocessor.

A har-bus® monoblock 47F with 220 terminals is used for the rear connector. This connector serves to connection into backplane module, which ensure distribution of all system and user signals across whole REMCS.

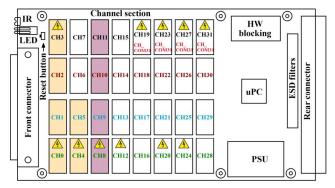

The Fig. 3 shows layout of key components on the PCB. The LED light pipes and IR transmitter/receiver are located above the front connector. A reset button is placed between light pipes and channel section. It serves to hardware reset of the microprocessor. The channel section of binary inputs and outputs contains 32 channels and it takes one half of PCB size. At the rear side (in Fig. 3, right side) of the PCB is situated a microprocessor that controls all binary channels and processes internal signals from the rear connector. The internal signals are filtered by ESD filters which precede EMC interferences among the plug-in cards through the backplane module. Above the microprocessor are hardware blocking circuits, and a local power supply unit (PSU) is located under the microprocessor.

Fig. 3. Layout of key components in the PCB of BIO card

#### IV. BINARY IO SECTION

The BIO section contains 32 channels. The hardware layout of individual channels in the PCB is designed for variant assembly of electronic components. Each channel can be configured as binary input or binary output. The individual channels are divided into some groups:

**Standard channels** – These channels are designed to operate with nominal voltage 24 V DC, they are not specially marked in Fig. 3.

**High voltage channels** – These channels have reinforced insulation in comparison with standard channels so it can work with voltage up to 150 V DC. The BIO card contains 11 150 V channels. These channels are marked with high voltage flash mark in Fig. 3.

**Channels with common potential** – These channels are related to the same potential which is marked CH\_COM31. It is group of channels: CH19, CH23, CH27 and CH31.

**Channels with Binary OUT blocking capability** – They are orange in color in Fig. 3. If this group of channels is configured as a binary output, the hardware blocking ability can be used to block them. These binary outputs are set to the required state (close or open) when the REMCS hardware blocking occasion appears. This blocking feature is not dependent on the microprocessor. The BIO card has six channels with binary OUT hardware blocking ability, where the three channels are 150 V outputs.

**Channels with Binary IN blocking capability** – The BIO card has four channels with binary IN hardware ability. One is a high voltage channel (Fig. 3, purple color). These binary inputs can control hardware blocking signals which block the

whole REMCS to the safe state. The hardware block occurs when the input signal changes from logical 0 to logical 1.

The binary inputs and outputs can be configured in several ways. This config feature ensures coverage of all industrial control voltage levels.

#### A. Binary outputs

The binary outputs can be configured in three ways: (i) Latched binary output, (ii) Non-latched binary output normally opened, (iii) Non-latched binary output normally closed. In all cases, relays with two contacts are used. The one contact creates power contact (binary output), leading to the front connector. The second contact is connected to the ADC via autodetection (described below) circuits. It serves as feedback of the state of binary output for the microprocessor.

### B. Binary inputs

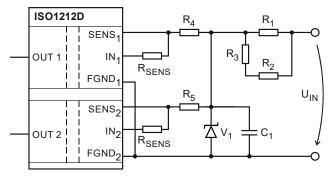

The binary inputs of the card are built from a digital isolator with two inputs – TI ISO1212D integrated circuit. Besides other digital isolators, in ISO1212D only a low voltage side has to be powered; therefore, an additional insulated power source is not required. It allows the creation of a hardware layout of binary inputs with smaller dimensions.

Fig. 4. Topology of binary input

Fig. 4 shows the topology of one binary input with ISO1212D. The voltage  $U_{IN}$  defines input voltage of binary input. The connection of resistors  $R_1$ ,  $R_2$ ,  $R_3$  results from the universal design of the channel. In case of binary input, the resistor  $R_3$  has jumper (zero Ohm), and parallel combination of  $R_1$  and  $R_2$  creates part of input voltage divider which is defined by level of input voltage  $U_{IN}$ . In case of binary output, these resistors defines type of output: normally opened or normally closed.

The voltage behind the input divider must not exceed 60 V because this value is limiting for ISO1212D. The limit is ensured by transil V<sub>1</sub>. Resistors  $R_{SENS}$  with resistor  $R_4$  or  $R_5$  creates low voltage divider for individual inputs of ISO1212D. These dividers are set to create low and high threshold. By this way the hysteresis of binary input is ensured.

#### V. AUTODETECION

Each channel has an autodetection circuit. The base of the autodetection circuit is the resistor R-2R network. A selected combination of the resistor is connected to an ADC that measures corresponding voltage on those resistors. According to connected accessories (ISO1212D for input or output latched relay, or output non-latched relay) the microprocessor (resp. control software) can recognize the channel configuration.

The autodetection routine is started when the power supply is turned on. The microprocessor uses ADCs which measure all analog feedback signals from all channels. After that the microprocessor defines configuration of individual channels based on the measured values. Table I shows recognition of configuration of channels based on the measured voltage  $U_{ADC}$ .

TABLE I.AUTODETECTION

| ISO1212D |       | Contact             | UADC                       | Conformation                          |  |

|----------|-------|---------------------|----------------------------|---------------------------------------|--|

| OUT 1    | OUT 2 | of binary<br>output | [V]                        | Configuration                         |  |

|          |       | opened 0.03         |                            | Non latched binary<br>output          |  |

| 0        | 0     |                     | 0.41                       | Binary input                          |  |

|          |       | opened              | 0.80                       | Latched binary output<br>Binary input |  |

| 0        | 1     |                     | 1.24                       |                                       |  |

| 1        | 0     | 2.06 E              |                            | Binary input                          |  |

|          |       | closed              | sed 2.49 Latched binary ou |                                       |  |

| 1        | 1     |                     | 2.89                       | 2.89 Binary input                     |  |

|          |       | closed              | 3.27                       | Non latched binary<br>output          |  |

#### VI. EXPERIMENTAL EVIDENCE

The prototype of BIO card is shown in the Fig. 5. During the first experiment were verified individual peripherals of the BIO card. All verifications were performed at laboratory temperature (25 °C) as well as in a climatic chamber where operating conditions were set to limit temperatures -40 °C and 70 °C. The PSU timing, dependent on the card address, was tested, and the delay of PSU turning on was tracked. The supply voltage levels 3.3 V and 1.2 V and their ripples were measured.

Fig. 5. The prototype of REMCS control system BIO card

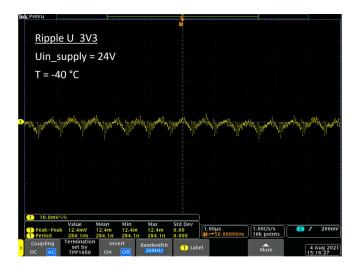

In Fig. 6, the detail waveform of the supply voltage 3.3 V during the temperature -40  $^{\circ}$ C is shown. The voltage ripple was 12.4 mV. For the temperature of 70  $^{\circ}$ C the voltage ripple remained the same.

Fig. 6. Voltage ripple of supply voltage 3.3 V at temperature -40 °C

The Table II indicates results of individual supply voltage levels dependence on temperature during the change of main supply voltage level. The supply voltage 3.3 V as well as supply voltage 1.2 V are stable during the change of main supply voltage from 16.8 V up to 32 V. It can be observed only little change in the voltage level 3.3 V which is caused by temperature.

TABLE II.

DEPENDENCE OF PSU VOLTAGE AT TEMPERATURE

|  | Uin_PSU<br>[V] | Temperat          | ure -40°C         | Temperature 70°C  |                   |

|--|----------------|-------------------|-------------------|-------------------|-------------------|

|  |                | Supply<br>3V3 [V] | Supply<br>1V2 [V] | Supply<br>3V3 [V] | Supply<br>1V2 [V] |

|  | 16,8           | 3,341             | 1,192             | 3,356             | 1,192             |

|  | 24             | 3,341             | 1,192             | 3,356             | 1,192             |

|  | 32             | 3,341             | 1,192             | 3,356             | 1,192             |

The channel section was also verified during the climatic tests. The function of the binary outputs was tested using IR debug interface. All binary outputs were exposed to the ON-OFF-ON sequence.

All thresholds across temperature range were monitored. There were tested 24 V inputs as well as 110 V inputs. The input voltage ranges were 0 - 32 V in case of 24 V binary inputs and 0 - 120 V in case of 110 V binary inputs during the tests. This also verified the possible overload of the binary inputs with 30 % of the nominal voltage.

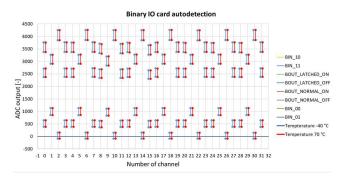

Fig. 7. Verifying of autodetection feature

One part of the testing of the channel section was also verification of autodetection and its reliability during the temperature change. In Fig. 7, it is captured a graph that represents measured values from ADC during the autodetection. Individual horizontal lines define the expected values of the configuration of the individual channels. Vertical lines represent ranges that are supplemented to specific measured values by the ADC. The blue vertical lines represent values measured in temperature -40°C, and the red vertical lines represent measurement in temperature of 70 °C. It is evident from this graph that the reserve among the individual configurations is sufficient.

#### VII. CONCLUSION

This paper focuses on designing a new generation of the BIO card of the REMCS control system. The BIO card was intended as the plug-in unit for the 3U sub-rack enclosure. The PCB of the BIO card fulfills the dimensions of the Eurocard format.

The BIO card contains 32 channels. Each channel can be configured to binary input or binary output. The individual channels can be divided into some groups: Standard channels, high voltage channels, channels with common potential, and channels with blocking ability. The high voltage channels can work with a voltage range up to 150 V DC. The autodetection routine can recognize the configuration of individual channels. The autodetection is based on hardware changes implemented to each channel's layout in the PCB. The card was tested under challenging operating conditions with temperatures in range from -40 °C up to 70 °C.

#### ACKNOWLEDGMENT

This research has been supported by the Ministry of Education, Youth and Sports of the Czech Republic under the project OP VVV Electrical Engineering Technologies with High-Level of Embedded Intelligence CZ.02.1.01/0.0/0.0/18\_069/0009855 and project SGS-2021-021.

#### References

- H. Akagi, "Multilevel Converters: Fundamental Circuits and Systems," in Proceedings of the IEEE, vol. 105, no. 11, pp. 2048-2065, Nov. 2017, doi: 10.1109/JPROC.2017.2682105.

- [2] M. Parchomiuk, R. Strzelecki, K. Zymmer and A. Domino, "Modular power converter topologies for energy storage and electric power distribution systems," 2017 Progress in Applied Electrical Engineering (PAEE), 2017, pp. 1-6, doi: 10.1109/PAEE.2017.8009022.

- [3] D. Woldegiorgis and A. Mantooth, "Investigation of a New Alternate Arm Modular Multilevel Converter Topology for HVDC Applications," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), 2021, pp. 290-295, doi: 10.1109/ECCE47101.2021.9595391.

- [4] H. Nademi, L. Norum and A. Das, "A new circuit of Modular Multilevel Inverter for grid-connected photovoltaic conversion plants," 2015 IEEE 42nd Photovoltaic Specialist Conference (PVSC), 2015, pp. 1-6, doi: 10.1109/PVSC.2015.7356398.

- [5] J. Štengl et al., "Distributed Control System for Medium-Voltage STATCOM based on Parallel Connected Power Converters," 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), 2021, pp. 307-311, doi: 10.1109/PEMC48073.2021.9432527.

- [6] L. Elis, P. Turjanica, L. Polacek and L. Piterka, "Evaluation of REMCS Control System for safety applications," 2014 22nd Telecommunications Forum Telfor (TELFOR), 2014, pp. 687-690, doi: 10.1109/TELFOR.2014.7034501.